단순한 Ungrounded FG-CPW 입니다.

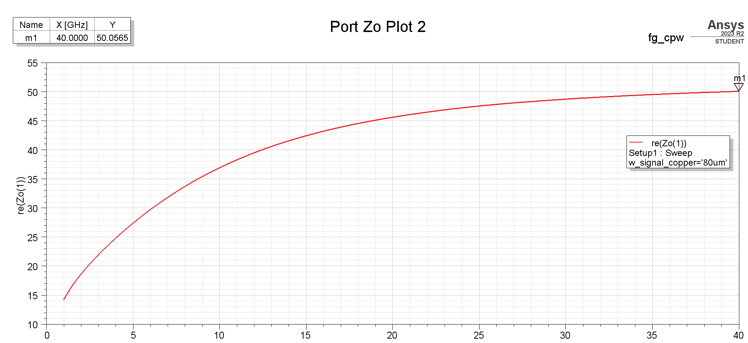

Silicon 기판(Si) 두께: 100um, SiO2 두께:700nm, Copper 두께: 1um로 설정하였으며 너비는 1mm, 길이는 540um 입니다. Signal 및 ground copper 너비는 80um, spacing은 40um 입니다.

Silicon wafer로 기판을 만들거라 라이브러리에 있는 Si에 bulk conductivity가 10S/만 바꾼 material(다른 특성은 동일)을 기판으로 사용했을 때 특성 임피던스가 기존과 다른 x축 대칭?인 그래프가 나오게됩니다. 50옴에 맞추려고 하는데 그래프가 반대로 나오는데 어떻게 해결할 수 있나요